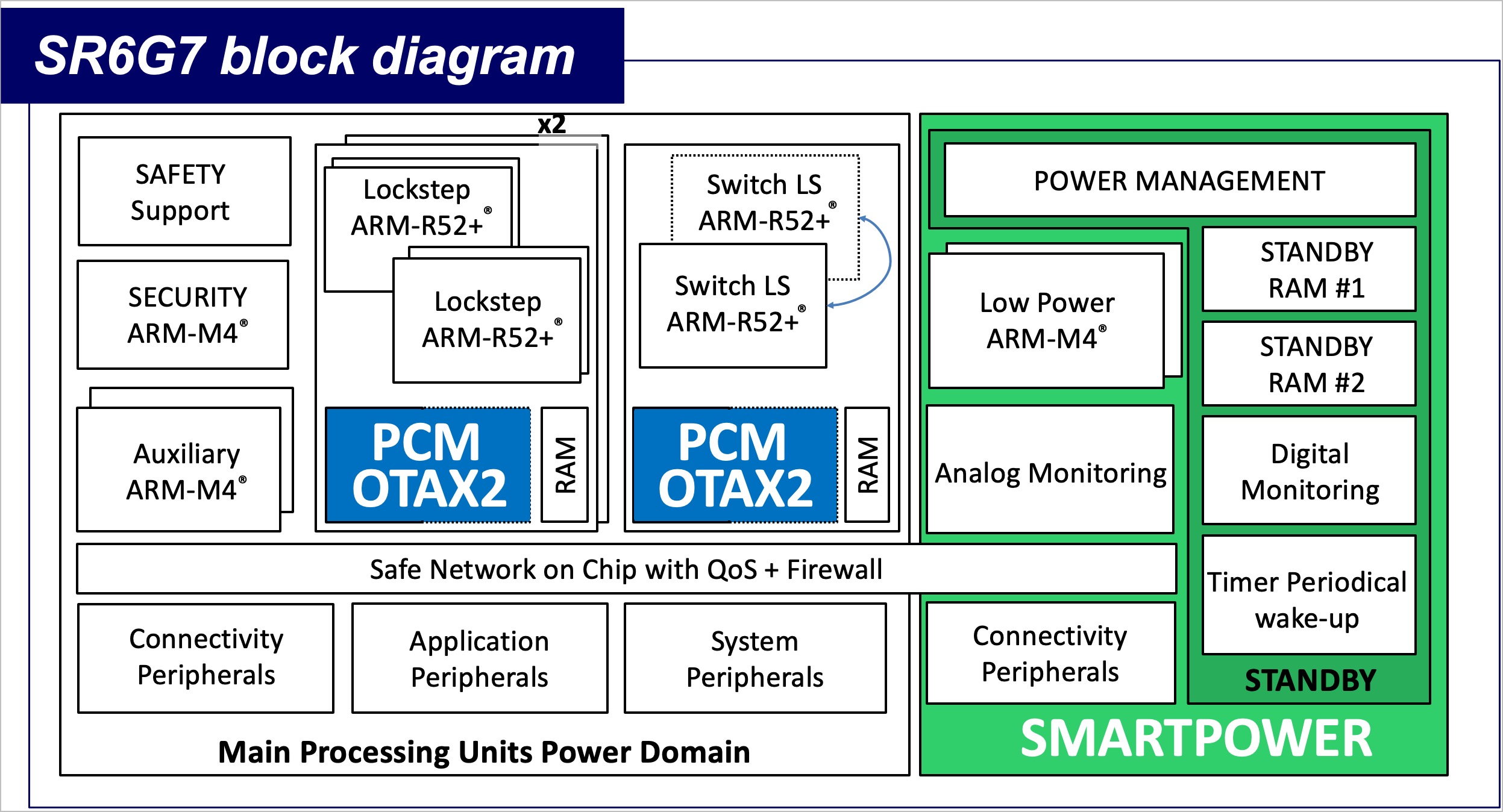

ST introduced the SR6G7, its new automotive-grade microcontroller with 21 MB of embedded phase-change memory (ePCM) at the 2023 Symposium on VLSI (very large-scale integration) Technology and Circuits (VLSI 2023 for short). We also held a demo showcasing how the 21 MB of ePCM can expand to 40.5 MB in full over-the-air (OTA) mode and how its SMARTPOWER feature uses a Cortex-M4 to enable flexible and feature-rich configurations while reducing the power consumption by a factor of more than 100. Moreover, the paper is highly symbolic because all its innovations will soon be available on the Stellar SR6G7 MCU, which is currently sampling.

OTA X2

How it started in 2021

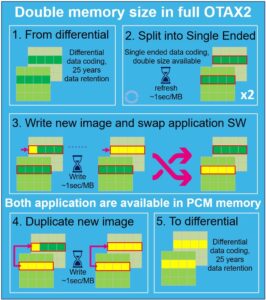

While the organizers behind VLSI 2023 will make the ST article available on IEEE Xplore, we wanted to review some of the critical innovations that pushed the judges to accept our paper. The breakthroughs are also a testament to our research and development strategies since this paper is the direct product of earlier work presented at VLSI 2021 on ePCM. Two years ago, we showed 16 MB of 28-nm ePCM using a cell size of 0.019 µm2. At the time, the paper described how it was possible to increase the memory capacity from 16 MB to 24 MB during over-the-air updates.

Expansion during OTA is possible thanks to the inherently rapid writing capabilities of ePCM. In 2021, the paper showed that it was possible to change the memory configuration from two cells per bit to a single cell using a built-in temporary buffer to update the memory content while an application is running transparently. 12MB out of 16MB of the memory size was actually doubled to 24MB, while 4MB remains used as a temporary buffer.

This buffer was about half the size of the available memory, so a 16 MB configuration would enjoy an 8 MB buffer for a total of 24 MB. At the time, the paper was hailed for its ability to overcome capacity limitations that often plagued automotive-grade MCUs, which led to serious complications when implementing OTA updates.

How it’s going in 2023

The 2023 paper builds on this previous research but introduces new built-in functionalities that no longer require an intermediate buffer. Indeed, the principle behind memory expansion is similar. Moving from a “differential mode” that uses two cells per bit to “single-ended” enables memory expansion. However, the new ePCM provides writing time slices as low as 35µs, thus allowing to split writing operations with very limited impact on the system, which means we can do away with the intermediate buffer. The system can use almost the entire memory in single-ended mode to reach a new capacity of 40.5 MB.

To make the innovation more meaningful to attendees, ST had a booth at VLSI to demo this new capability. The GUI showed whether the ePCM was in differential or single-ended mode. It also demonstrated how the software could use the latter to load a new image in the background, swap it to make it active, and then duplicate it before reverting to differential mode. And since the demo runs on the Stellar SR6G7, attendees knew the technology would be commercially available in the near future, thus allowing companies to implement it in real-life systems.

SMARTPOWER

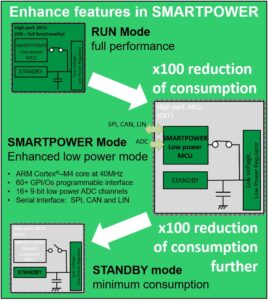

Another key technology showcased at the ST demo booth and in the paper is SMARTPOWER, a new power management mechanism capable of powering a low-consumption cortex-M4 subsystem embedded into the larger MCU. Increasingly, designers need low-power modes with greater functionalities. For instance, the ability to collect sensor data at all times is no longer optional. The problem is that keeping so many peripherals active means that a significant portion of the MCU must remain awake, limiting the possible power savings. Furthermore, this particular challenge will only get trickier over time. As software-defined vehicles continue to transform our cars, electronic control units (ECUs) will necessitate more powerful microcontrollers while users will always clamor for more power savings.

SMARTPOWER brings an original new solution by enabling the system to switch to an embedded MCU within the MCU! In this instance, the Cortex-M4 can drive SPI, CAN, and LIN interfaces at a fraction of the power consumption. Obviously, moving from using the Cortex-R52+ to the single Cortex-M4 is no small feat.

In a nutshell, the system must switch to a new power domain, which means dealing with the leftover energy from capacitors while ensuring fast wake-up times when reverting to the more powerful system. To accomplish this, ST worked on a new topology and implementation of the switching mechanism. In the demo, we showed how we transition from one core to the next without interrupting communication with a PC using UART/LIN.

FBB

Finally, the paper introduces an innovative usage of forward body biasing (FBB) that tunes the die’s characteristics to ensure optimum performances across the full temperature range while minimizing consumption, especially at high temperatures. Traditionally, devices use a dynamic voltage scaling system. The challenge with such an approach is that it uses a continuous loop with external regulators to adjust the voltage constantly.

Consequently, the system may suffer from safety issues or a reduction of the product’s lifespan when applying high voltages. FBB solves this by providing a system that works entirely within the silicon to find the balance between temperatures, performance, and voltages. Besides greater robustness, FBB also reduces leakage at high temperatures, thus offering a far more convincing alternative to dynamic voltage scaling in automotive applications.